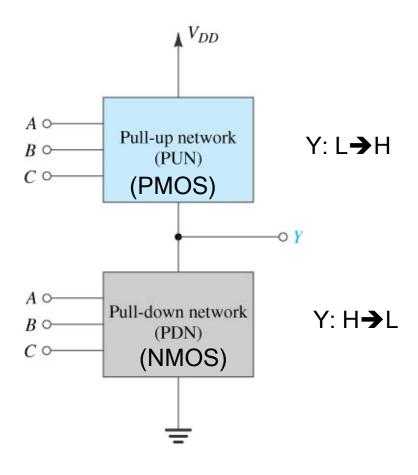

## Lect. 21: CMOS Logic Gates (S&S 10.3)

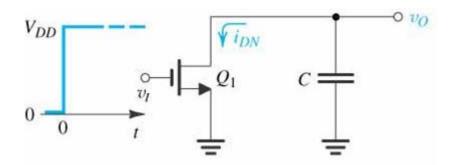

Pull Down

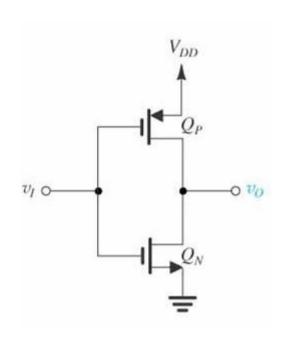

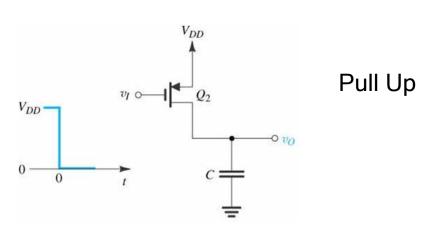

#### **CMOS** inverter

Different transistor acting for pull-down and pull-up operation (NMOS) (PMOS)

### **CMOS Logic Gates**

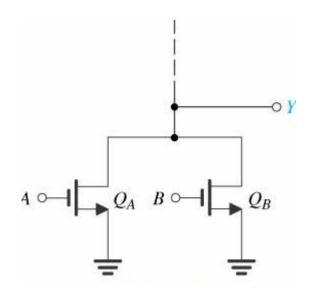

#### Examples of pull-down networks

Y pull-down, if A high OR B high

ightharpoonup Q<sub>A</sub> or Q<sub>B</sub> ON

For Y pull-up, A low AND B low

$\rightarrow$  Q<sub>A</sub> and Q<sub>B</sub> OFF

Logic Operation:  $\overline{Y} = A + B$

→ NOR Gate

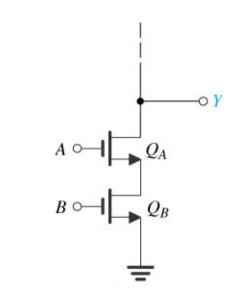

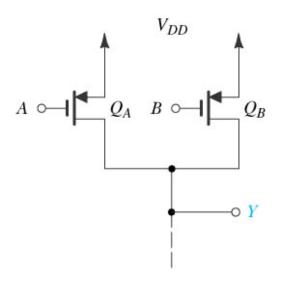

#### Examples of pull-down networks

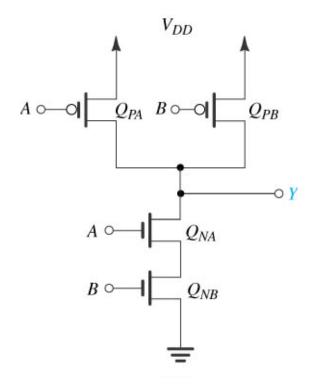

Y pull-down, if A high AND B high

$\rightarrow$  Q<sub>A</sub> and Q<sub>B</sub> ON

For Y pull-up, A low OR B low

$\rightarrow$  Q<sub>A</sub> or Q<sub>B</sub> OFF

Logic Operation:  $\overline{Y} = AB$

→ NAND Gate

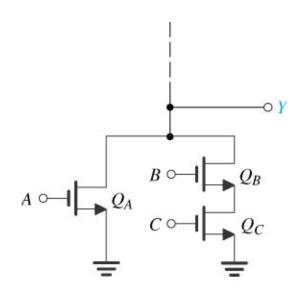

### Examples of pull-down networks

$$\overline{Y} = A + BC$$

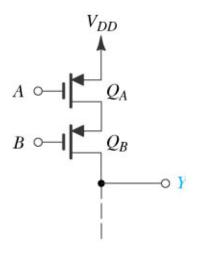

#### Examples of pull-up networks

Y pull-up, if A low OR B low

$\rightarrow$  Q<sub>A</sub> or Q<sub>B</sub> ON

For Y pull-down, A high AND B high

$\rightarrow$  Q<sub>A</sub> and Q<sub>B</sub> OFF

Logic Operation:  $Y = \overline{A} + \overline{B}$

→ NAND Gate

#### Examples of pull-up networks

Y pull-up, if A low AND B low

$\rightarrow$  Q<sub>A</sub> and Q<sub>B</sub> ON

For Y pull-down, A high or B high

$\rightarrow$  Q<sub>A</sub> or Q<sub>B</sub> OFF

Logic Operation:  $Y = \overline{A}\overline{B}$

→ NOR Gate

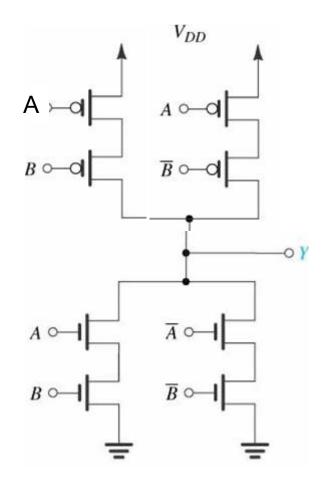

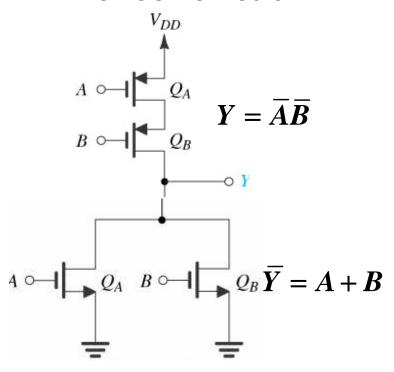

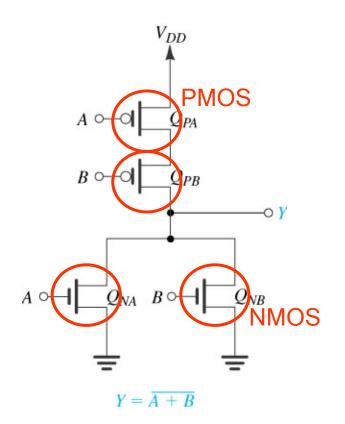

#### **CMOS NOR Gate**

PUN: complemented input

PDN: complemented output

Structures of PUN and PDN have the duality property

**CMOS NAND Gate**

CMOS XOR (Exclusive OR)

A: 0 1 0 1

B: 0 0 1 1

XOR: 0 1 1 0

$$Y = A\overline{B} + \overline{A}B \rightarrow PUN$$

$$\overline{Y} = AB + \overline{A}\overline{B}$$

$\rightarrow$  PDN